Sundance DSP’s sFPDP IP core provides a highly flexible interface to support communication with external devices or other FPGAs using the ANSI/VITA 17.1 Serial Front-Panel Data Port protocol.

sFPDP enables high-speed, low-latency serial communication at rates up to 2.5Gb/s or more, with optional CRC, flow control and data framing, as well as a number of asynchronous control bits. FC120 provides a fast, robust replacement for parallel FPDP while at the same time simplifying the cabling requirements

Features

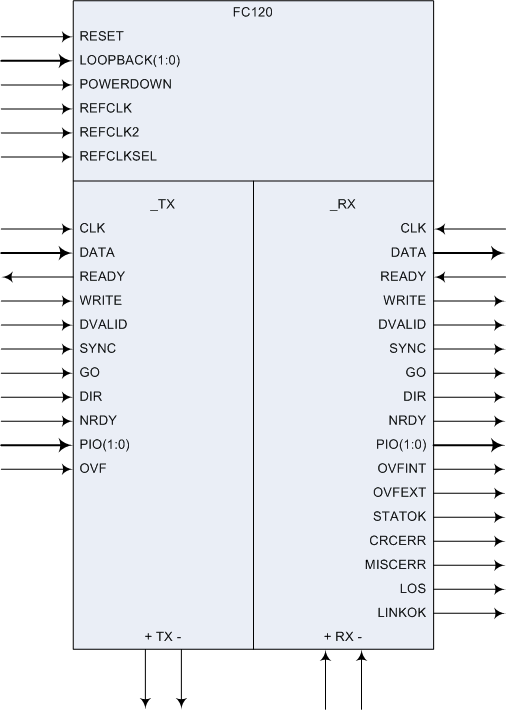

- Bidirectional or Unidirectional interfaces supported

- Optional CRC

- Optional flow control prevents data loss

- Supports standard sFPDP line rates of 1.0625, 2.125, and 2.500Gb/s as well as non-standard rates between 1.000-3.125Gb/s

- Support for rates from 600Mb/s-1.000Gb/s may be added by special request, higher rates may be available with some FPGAs

- May be used with copper or optical interfaces

- Includes asynchronous FPDP sideband signals: PIO1, PIO2, DIR, NRDY

- The FPGA transmit and receive data interfaces are independently clocked, no specific relationship to the bitrate is required

- Virtex2-Pro and Virtex4 currently supported, Virtex5 in development

- Adjustable drive strength and pre-emphasis to handle a wide range of transmission characteristics

- Reference clock is run-time selectable from two sources

- User-selectable inversion of TX and/or RX differential pairs

- 32-bit data interface in both directions

FC120 may be provided as a stand-alone VHDL module or as a 3L/Diamond-compatible task. Several independent FC120 modules may be instantiated at the same time, limited only by the number of SerDes modules provided by the FPGA.