Certified 64 bits capable DES and triple-DES 64 bits Crypto Core

The NES-IPCORE-TDES offers robust security for your communication needs. Built on the foundation of the Data Encryption Standard (DES), but with enhanced complexity, it delivers a more secure “Triple-DES” solution. Think of it as a triple wall protecting your data compared to DES’s single wall.

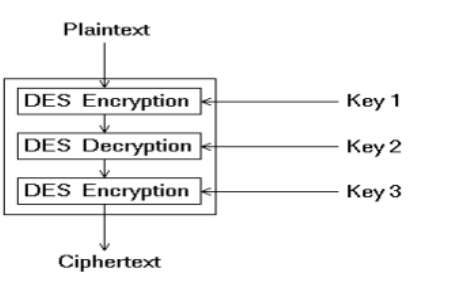

This IP core achieves its strength by using three DES operations in a specific sequence. Imagine encrypting your data three times, each with a different key, making it significantly harder for unauthorized access. Decryption follows the same principle, ensuring only authorized parties can unlock the message.

Whether you’re safeguarding sensitive information in government, finance, or healthcare sectors, the NES-IPCORE-TDES provides peace of mind and compliance with industry standards. Its compact design and efficient implementation make it suitable for various embedded systems and hardware platforms.

Upgrade your security with NES-IPCORE-TDES and experience the power of Triple-DES protection.

Features

-

The core performs a classical modular exponentiation of X y mod m

-

The core performs Ek3(Dk2(Ek1(I))) = O encryption and Dk1(Ek2(Dk3(O))) decryption, where Ek(I) and Dk(I) denote DES decryption of I using DES key k, respectively.

-

Direct access to all registers

-

Can be customized

-

The NES-IPCORE-TDES is a Triple-DES which is an extension of Data Encryption Standard (DES) that results in a more complex but more secure block cipher. Standard DES represents a component in the Triple-DES architecture.

-

If Ek(I) and Dk(I) denote the DES encryption and decryption of I using DES key k, respectively, then Triple-DES encryption and decryption are performed as follows:

-

Encryption: Ek3(Dk2(Ek1(I))) = O

-

Decryption: Dk1(Ek2(Dk3(O))) = I

-

-

Any other pre-designed functions can be integrated into the FPGA.

-

FPGA density and I/O requirements can be defined according to customer specifications.

-

Designers should be familiar with cryptographic standards, VHDL, synthesis tools, FPGA Place and Route data flow and VHDL simulation software.

-

Experience with microprocessors is recommended.

-

The macro can easily be integrated into hierarchical VHDL designs.

| NES-IPCORE-TDES | Certified 64 bits capable DES and triple-DES 64 bits Crypto Core |