The following features are controllable by software:

- Input signal range, coupling, termination and offset adjustment

- Self-calibration

- Sampling clock selection

- Direction of external trigger in/out

- ADC configuration and status

The offset adjustment does not clip the signal at the highest range (+/- 5V). That is why the “max input signal amplitude” has been specified as 10V, even though the selection of signal ranges only goes up to 5V. This way, a +10V pulse with -5V offset could still be digitised without clipping.

The sampling clock is derived from a voltage-controllable 125MHz clock source, controlled via an SPI DAC.

A copy of the 125MHz clock source is available on the FMC connector pins.

Software can select either one of the input channels to be sampled at 2 GSPS, by interleaving the 2 ADCs.

50 Ohm input is protected from overload

8 channel 12 bit I2C ADC monitors all local power supplies

This is a product that was developed in conjunction with CERN’s Open Hardware Repository and is available as a project here. The CERN Open Hardware Licence is to hardware what the free and open-source licences are to software. It defines the conditions under which a licensee will be able to use or modify the licensed material. It shares the same principles as free software or open-source software: anyone should be able to see the source – the design documentation in the case of hardware – study it, modify it and share it.

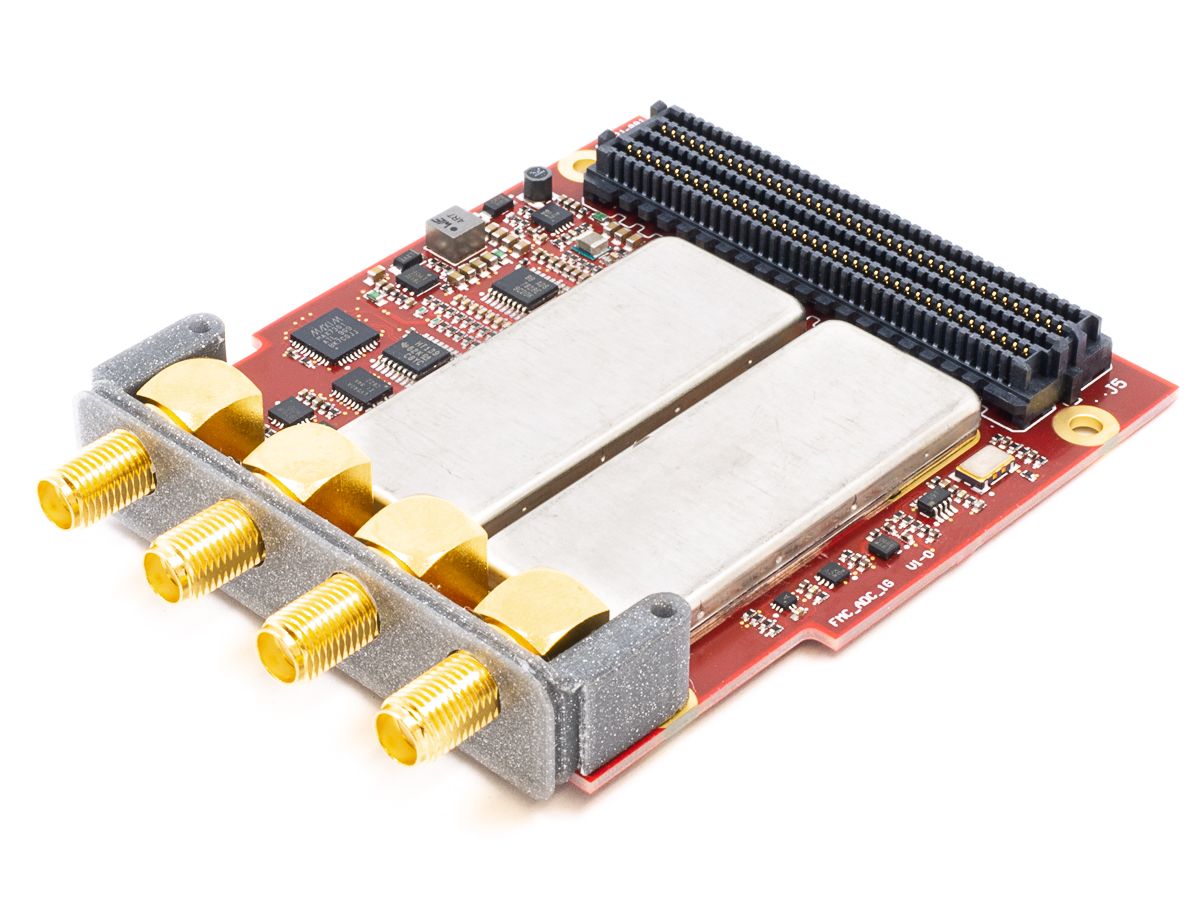

PCB Format: VITA 57.1 FMC LPC

Connectors: SMA

Sampling Rate: 1 GSPS (2GSPS in single channel mode)

Input Signal Type: Single-ended

Resolution: 8 bits

Number of Channels: 2

Bandwidth (-3dB): 50Ω: DC to 400MHz (or better), 1MΩ: DC to 300MHz (or better)

Input Signal Coupling and Termination: AC (8 Hz LF limit, after 50 Ω termination), DC-50Ω, DC-1MΩ

Input Signal Range: +/- 50mV, +/- 250mV, +/- 500mV, +/- 2.5V, +/- 5V

Max Input Signal Amplitude: +/- 10V

SNR: > 40dB full bandwidth over all input ranges

ENOB: > 6.5 full bandwidth over all input ranges

Offset Adjustment Range: +/- 5V

Offset Adjustment Resolution: 16 bits

Offset Adjustment Accuracy: < 1%

Additional I/O: External TTL trigger in/out (bidirectional), External 10MHz clock input

Self-calibration: Automatic zeroing of offset and gain

ADC Interface: serial/parallel LVDS

Temperature Sensor: On I2C bus

FMC EEPROM: 32K bits type 24C32

Power Consumption: Design estimation 9.6W