Unlocking Powerful Encryption with NES-IPCORE-RSA

The NES-IPCORE-RSA offers unparalleled security and flexibility for your encryption needs. Boasting support for a massive range of key sizes (from 512 to a staggering 4096 bits!), it surpasses common standards and delivers exceptional protection for sensitive data.

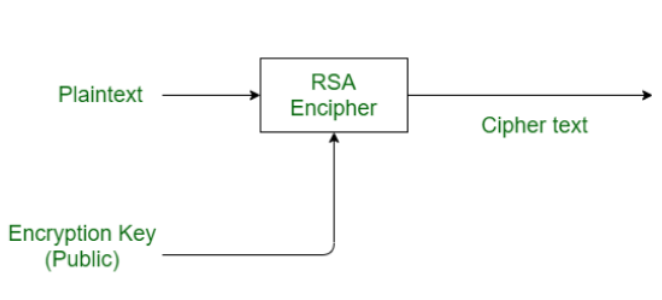

Imagine safeguarding information with keys multiple times longer and more complex than industry norms. This core performs the core encryption technique known as “modular exponentiation,” utilizing powerful mathematical operations to scramble your data into an unreadable format. Only those with the corresponding key can unlock the secrets it holds.

The NES-IPCORE-RSA isn’t just strong, it’s adaptable. Choose the key size that best suits your security requirements, from 512 bits for everyday protection to 4096 bits for top-secret information. Plus, it seamlessly integrates into your existing systems – requiring only 4 memory cores and offering direct register addressing for easy control.

But power doesn’t stop there. This core is built for customization. Need additional encryption functions? No problem! Want to optimize it for specific FPGA hardware? We’ve got you covered. Just tell us your needs, and we’ll tailor the core to your exact specifications.

Empower your security with NES-IPCORE-RSA and experience the freedom of customizable, high-performance encryption.

Features

- Certified 512-4096 bits capable RSA Crypto Core

- The core performs a classical modular exponentiation ^ where x is the plain text input which will be ciphered, y is the key input and the

module m input - Support all key sizes (512, 1024, 2048, 4096) and includes a complete testbench

- Required 4 memory cores: One single-port RAM and three FIFOs

- Direct addressing of all Registers

- Can be customized

- Any other pre-designed functions can be integrated into the FPGA.

- FPGA density and I/O requirements can be defined according to customer specifications.

- Designers should be familiar with cryptographic standards, VHDL, synthesis tools, FPGA Place and Route data flow and VHDL simulation software.

- Experience with microprocessors is recommended.

- The macro can easily be integrated into hierarchical VHDL designs.

| NES-IPCORE-RSA | Certified 512-4096 bits capable RSA Crypto Core |