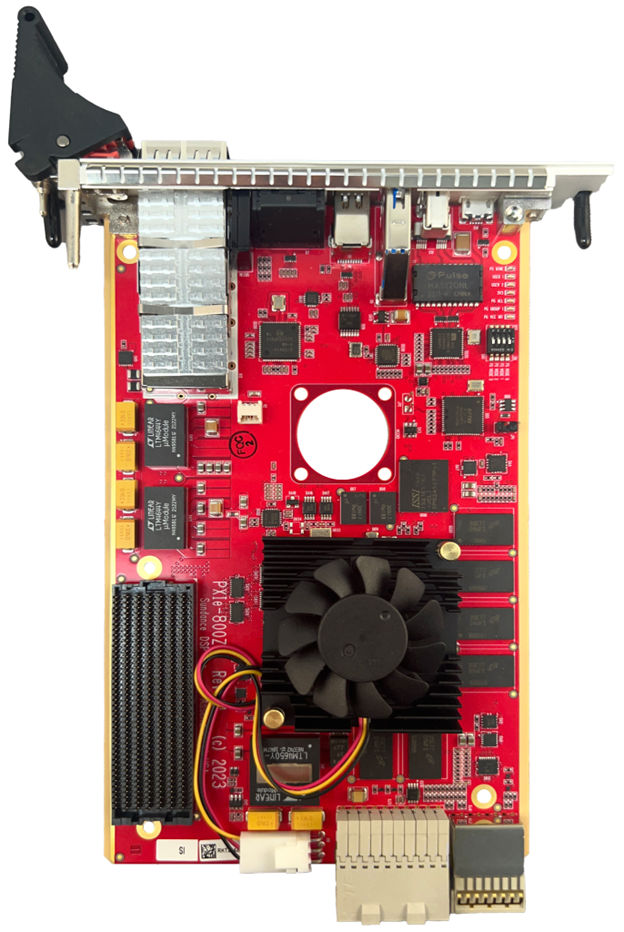

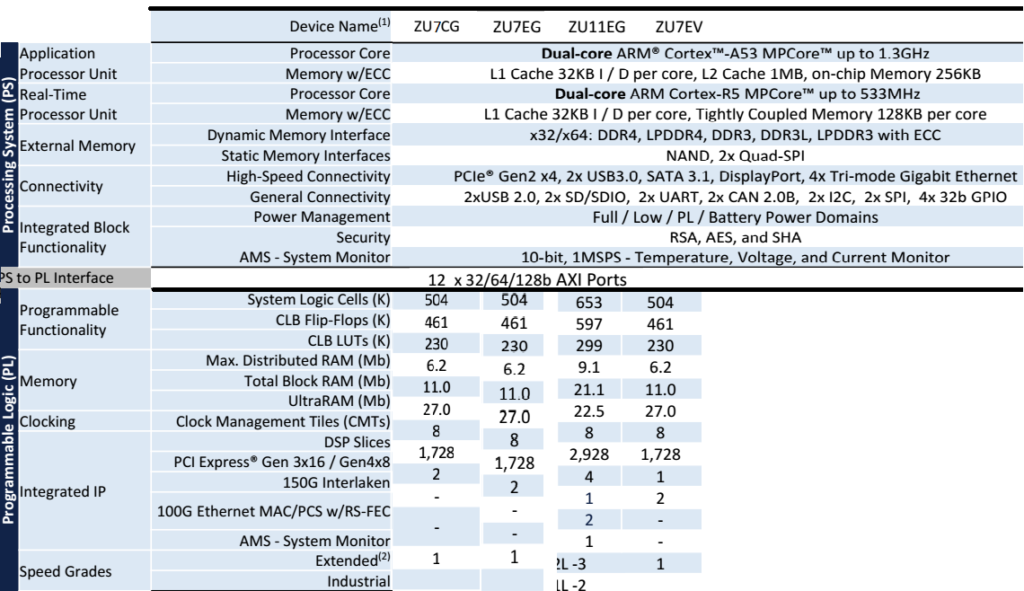

PXIe800Z supports AMD Zynq UltraScale+ MPSoC FPGA family and complies with PXIe standard.Depending on the choice of FPGA (XCZU7EV / XCZU7EG/ XCZU11EG / XCZU7CG in C1156 package) it can be used for High-Performance Computing (HPC), digital communication or image processing, including AR/VR applications. The selection of FPGA used on this board and their available resources are shown below.

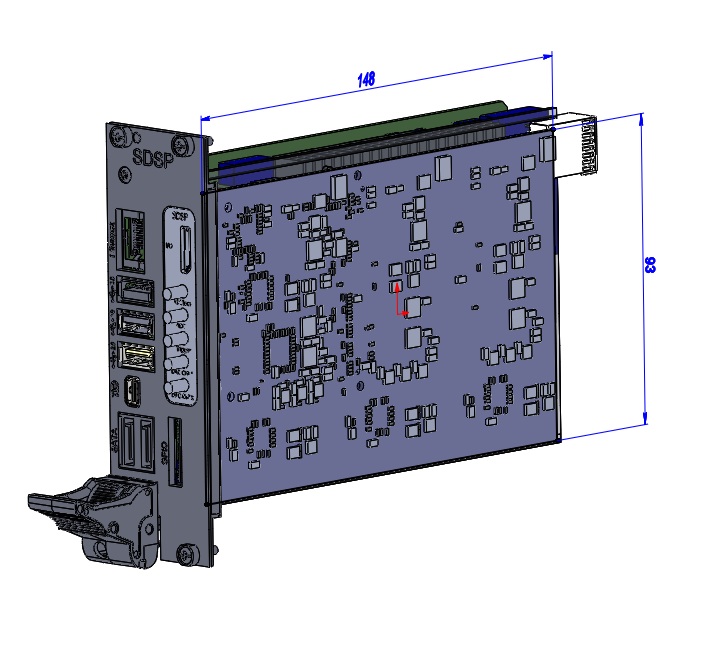

The platform can take standard FMC (rev 2.0 with FMC+) based hardware or custom size FMC ( (rev 2.0 with FMC+) hardware solution which offer much larger PCB area for design and front panel area for placing IO interfaces (see the size and format of custom FMC ( (rev 2.0 with FMC+) in the Additional Images’ tab). This makes the hardware particularly suitable for high-end test and measurement applications with custom FMCs which we can help design.

If no FMC daughter card (rev 2.0 with FMC+) is used then the solution will occupy only one slot and when an FMC ( (rev 2.0 with FMC+) is added then it will become a 2 slots solution. The hardware has the external power connector and can be used as an embedded solution without needing a host.

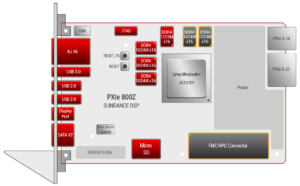

This PXIe card comes with QSFP+, FMC+, ethernet, display port, USB and SATA interfaces.

Summary of devices and available resources:

Rev2.0 of PXIe800Z is released and available with some changes to rev1.1. Both revisions can be purchased. See features tab for changes.

Features

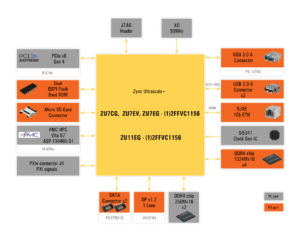

- x1 HPC FMC expansion site with 10 GTH at 16.3Gb/s transceivers and 56 LVDS IO pairs (rev 2 of the board uses FMC+ with 16 GTH)

- Can use extra large FMC modules for custom application

- Zynq Ultrascale+ MPSoC FPGA in C1156 package (XCZU7EV / XCZU7EG/ XCZU11EG / XCZU7CG)

- 4GB of DDR4 to PL

- Flash memory for user application bitstream

- Micro SD card for running OS and embedded applications (attached to PS part).

- JTAG connector

- System monitoring

- x8 lanes PCIe Gen4

- Video Codec H.265/H.264 with XCZU7EV

- GTH, GTY, 100EMAC and Interlaken, when fitted with XCZU11EG

- for the ARM processors within the Zync following interfaces are available:

- Display port

- 2x SATA

- 1x CAN

- Up to 8 GB of SDRAM to PS

- 1 x USB3

- 2 x USB2

- 2 x SATA

- 1 x RJ45

For Rev2.0 the following changes have been made to rev1.1

- ETH, USB PHY controls moved to PS,

- added GPIO I2C, i2C mux,

- FMC+ controls moved to PS,

- I2C FMC moved to PS,

- USB-JTAG now USB bus Powered.,

- Added EEPROM,

- FAN by default now at maximum RPM,

- FMC+ JTAG included into JTAG

- Crystals and XOs changed to Transko parts.

- PL UART relocated to Header,

- Added back BOOT MODE FTDI control,

- Added jumper to override FMC JTAG

Applications

- Defense

- Medical Imaging

- Machine Vision

- Stereo vision

- Artificial Reality /Augmented Reality

- Control

- Instrumentation and testing

- Software Defined Radio

- Data capture and logging

Additionally, depending on the device fitted (CG, EG or EV) to the PXIe800Z, different set of applications cane be better suited for the board as shown below. Different form factors of this design, based on PCIe and PCIe104, are also available which can be preferable for an application.

| CG | EG | EV |

| • Sensor Processing & Fusion • Motor Control • Low-cost Ultrasound • Traffic Engineering |

• Flight Navigation • Missile & Munitions • Military Construction • Secure Solutions • Networking • Cloud Computing Security • Data Center • Machine Vision • Medical Endoscopy |

• Situational Awareness • Surveillance/Reconnaissance • Smart Vision • Image Manipulation • Graphic Overlay • Human Machine Interface • Automotive ADAS • Video Processing • Interactive Display |

|

|

|

|

|

|

|

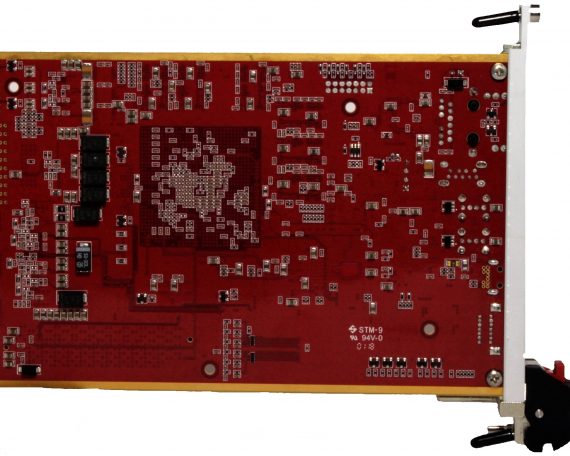

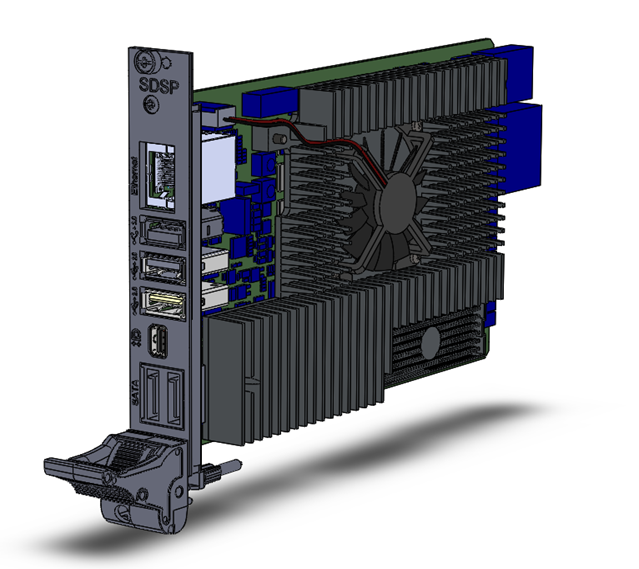

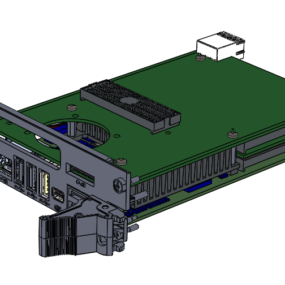

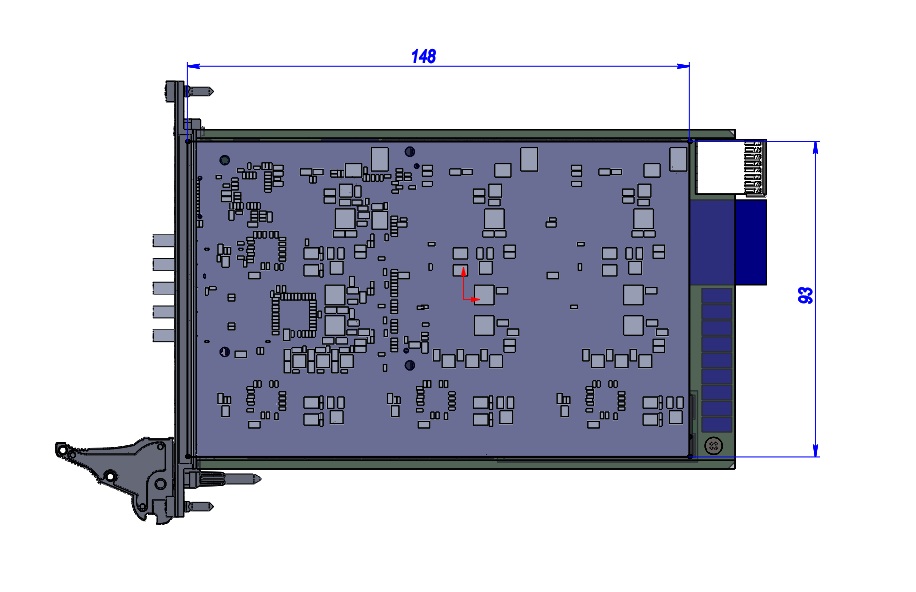

| Component side of PXIe800Z | Solder side of PXIe800Z | PXIe800Z without FMC Carrier | PXIe800Z+FMC carrier | Frontal view of PXIe800Z+FMC carrier | PXIe800+Extra large FMC | Dimensions of Extra large FMC |

PXIe800Z block diagram rev2.0

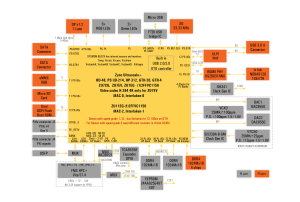

PXIe800Z placement rev1.1

PXIe800Z placement rev1.1

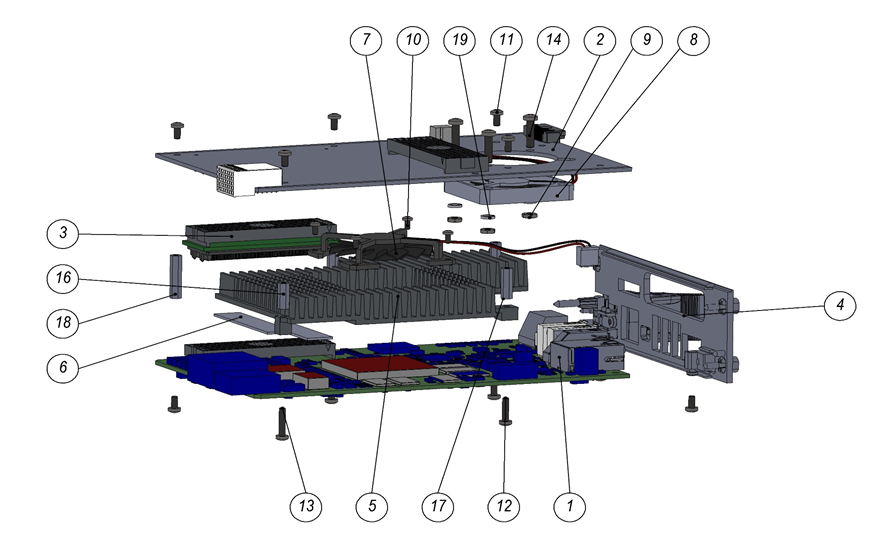

Exploded view of PXIe800Z + inter-poser and FMC carrier. It also shows the heat sink.

Exploded view of PXIe800Z + inter-poser and FMC carrier. It also shows the heat sink.

| 1 | PXIe800Z board | 1 |

| 2 | PXIe800Z-FMC board | 1 |

| 3 | PXI800Z interposer board | 1 |

| 4 | Front panel 3U 4HP | 1 |

| 5 | Heatsink | 1 |

| 6 | Thermal Pad thickness 1mm | 1 |

| 7 | FAN 45x45x10mm Evercool EC4510M12S-X | 1 |

| 8 | FAN 40x40x6mm Orion OD4006-12HSS | 1 |

| 9 | Nut DIN 439 M3 | 3 |

| 10 | Screw DIN 7985 – M2 x 4 | 4 |

| 11 | Screw DIN 7985 – M2.5 x 5 | 16 |

| 12 | Screw DIN 7985 – M2.5 x 10 | 4 |

| 13 | Screw DIN 7985 – M2.5 x 12 | 1 |

| 14 | Screw DIN 7985 – M3 x 12 | 3 |

| 15 | Post 10 M2.5 | 2 |

| 16 | Post 11.1 M2.5 | 1 |

| 17 | Post 13,1 M2.5 | 3 |

| 18 | Post 18.6 M2.5 | 1 |

| 19 | Washer DIN 7980 M3 | 3 |

A full BSP including Buildroot Linux for the Zynq UltraScale+ is included. Host-side Linux and Windows PCIe DMA drivers are also supplied.

PXIe800z-revA.B-YYYYX

where revA.B can be 1.1 or 2.0 (rev 1.1 has resets for USB, Ethernet, and FMC I2C control from the PL side, rev 2.0 has these signals moved to the PS side). Default is 1.1. For full details please see features tab.

where YYYY can be 11EG, 7EV, 7CG, or 7EG representing the FPGA type of the Zynq Ultrascale+ in the FFVC1156 package. Default is 7EV

where X can be E or I representing Extended or Industrial temperature grade. Default is E

All PXIe800z are built with -2 speed grade components. Contact SDSP support if another speed grade is required.