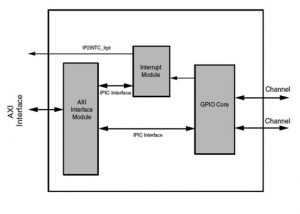

The FC-GPIO IP core has two clock domains. All registers except RGPIO_IN are in system clock domain. RGPIO_IN register can be clocked by system clock or by external clock reference.

The FC-GPIO IP Core has several software accessible registers. Most registers have the same width as number of general-purpose I/O signals and they can be from 1 – 32 bits. The host through these registers programs type and operation of each general-purpose I/O signal.

The core is delivered integrated and verified and is provided with a Testbench The FC-GPIO can be customized please contact our sales team for more information.

Features

- Number of general-purpose I/O signals is user select-able and can be in range from 1 to 32.

- For more I/Os several GPIO cores can be used in parallel.

- All general-purpose I/O signals can be bi-directional

- All general-purpose I/O signals can be three-stated or open-drain enabled